商品详情

深度融合计算机算法分析与设计、人工智能、面向对象程序设计等内容。

融入国际顶级期刊和会议研究论文与课题组多年成果,涵盖芯片测试与安全的最新技术趋势。

设计软件仿真与硬件实验环节,为有兴趣的学生提供实践机会,增强动手能力。

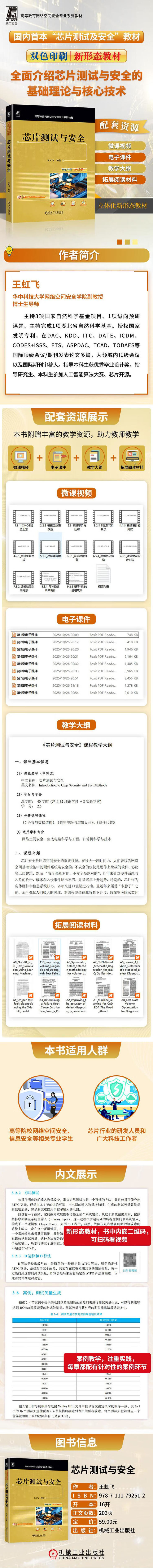

配套提供电子课件、知识点视频、教学大纲、拓展阅读材料。

融入国际顶级期刊和会议研究论文与课题组多年成果,涵盖芯片测试与安全的最新技术趋势。

设计软件仿真与硬件实验环节,为有兴趣的学生提供实践机会,增强动手能力。

配套提供电子课件、知识点视频、教学大纲、拓展阅读材料。

本书全面介绍了芯片测试与安全的基础理论与核心技术,包括故障模型、测试矢量生成、可测试性设计、扫描设计和内建自测试,重点分析故障仿真与诊断方法。本书讨论了存储器测试、时延测试等关键技术,并结合全球化供应链背景,探讨芯片经济学、安全问题及硬件IP保护。本书详细解析了物理攻击与防篡改技术,介绍了侧信道攻击类型及防御策略,深入讲解了物理不可克隆函数的原理与攻防技术,以及逻辑锁定等安全增强技术的应用。本书还探索了结合人工智能提升芯片测试效率与安全性的路径。章后配有习题,以指导读者深入学习。第10章配有电子设计自动化测试与安全实验,为读者提供动手实践机会。

本书适合作为高等院校网络空间安全、集成电路、计算机科学与技术、电子信息工程等相关专业高年级本科生、研究生的教材,也可供芯片测试与安全行业的研发人员和广大科技工作者参考。

本书适合作为高等院校网络空间安全、集成电路、计算机科学与技术、电子信息工程等相关专业高年级本科生、研究生的教材,也可供芯片测试与安全行业的研发人员和广大科技工作者参考。

王虹飞,华中科技大学网络空间安全学院副教授,博士生导师。主要研究方向包括人工智能芯片系统研发、芯片EDA、硬件安全、人工智能理论算法设计。主持3项国家自然科学基金项目、1项纵向预研课题、主持完成1项湖北省自然科学基金。在美国半导体研究联盟(SRC)课题中负责EDA关键技术研发。曾就职于英特尔研究中心(匹兹堡)、卡内基梅隆大学(CMU)先进芯片测试实验室。授权国家发明专利,在DAC、KDD、ITC、DATE、ICDM、CODES+ISSS、ETS、ASPDAC、TCAD、TODAES等国际顶级会议/期刊发表论文多篇,为领域内顶级会议以及国际期刊审稿人。研究获得工业界关注,受到半导体头部企业资助正在开展密切合作研发。指导本科生获优秀毕业设计奖,指导研究生、本科生参加人工智能算法大赛、芯片开源设计大赛、信创大赛人工智能赛道等获奖。指导毕业生就职于IT头部企业或在世界一流大学攻读博士学位。

前言

第1章概论

11集成电路

12数字集成电路

121组合逻辑电路

122时序逻辑电路

13芯片产业

131CMOS制造工艺

132连线

133封装

14芯片测试

15电子设计自动化

151电子设计自动化与电子设计自动化软件

152电子设计自动化软件的应用与研发

16芯片安全

161硬件安全

162芯片供应链安全

163芯片安全的挑战

164网络空间中的芯片安全

17测试与安全

171芯片测试从理论和技术上支持芯片安全

172芯片安全促进测试

18习题

第2章数字芯片故障模型

21物理缺陷与故障模型

22数字电路故障模型

221固定型故障模型

222晶体管闭合与开路故障模型

223桥接型故障模型

224输入模式故障模型

23故障等价与压缩

24案例:故障压缩

25习题

第3章数字芯片测试与故障仿真

31测试矢量生成

32组合逻辑电路测试矢量生成

321随机测试矢量生成

322穷尽测试

323D运算和D算法

324PODEM

325FAN

33时序逻辑电路测试矢量生成

331时间帧展开

332基于仿真的方法

34可测试性度量

341SCOAP

342COP

343高层次可测试性度量

35故障仿真与诊断

351串行故障仿真

352并行故障仿真

353并行矢量故障仿真

354推演故障仿真

355并发故障仿真

356差分故障仿真

36故障诊断

37故障元胞

38案例:测试矢量生成

39习题

第4章数字芯片可测试性设计

41扫描设计

411扫描单元

412扫描设计的流程

413扫描设计的测试

414扫描设计的测试矢量生成

42内建自测试

421测量矢量生成

422输出响应分析

423BIST设计规则

424BIST架构

43边界扫描

431测试访问端口

432TAP控制器

433寄存器和指令译码器

434指令

44习题

第5章其他数字芯片关键测试技术

51存储器测试

511存储器与测试之间的联系

512存储器故障

513存储器测试方法

52IDDQ测试

521IDDQ测试原理

522IDDQ测试方法

523适用故障范围

53时延测试

531延迟故障模型

532时延测试方法

54习题

第6章硬件攻击与芯片安全

61芯片供应链安全

611芯片供应链

612安全隐患及对策

62硬件IP设计与安全

621硬件IP分类

622安全隐患

63侧信道攻击

631侧信道攻击分类

632攻击方法

64面向测试的攻击

641基于扫描的攻击

642基于JTAG标准的攻击

65硬件木马

651硬件木马结构

652硬件木马分类

653防御措施

66其他物理攻击

661逆向工程

662探测攻击

663PCB攻击

67习题

第7章数字芯片的安全增强技术

71硬件混淆概述

711硬件混淆的目的

712不同层级的混淆

72混淆技术

73逻辑锁定

731设计方法

732攻击方法

74习题

第8章物理不可克隆安全芯片

81硬件安全原语

811物理不可克隆函数

812真随机数生成器

813防伪设计

82PUF的种类与应用

821PUF的分类

822PUF的评估指标

823设备认证

824密钥生成

83PUF设计

831仲裁器PUF

832异或APUF

833插入式PUF

834多路选线器PUF

835轻量级安全PUF

836前馈仲裁器PUF

837环形振荡器PUF

838双稳态环PUF

839静态随机存储器PUF

8310蝴蝶PUF

84面向PUF的攻击方法

841物理攻击方法

842建模攻击方法

843抵御建模攻击的手段

85面向PUF的可靠性攻防分析

86案例:基于FPGA的双稳态PUF硬件设计

87习题

第9章人工智能时代的数字芯片测试与安全

91前沿研究1:机器学习助力芯片测试与诊断

92前沿研究2:面向PUF的人工智能建模攻击

921基于CP分解的张量神经网络攻击

922基于神经网络计算图的近似建模攻击

923基于深度神经网络的建模攻击

924结合侧信道信息的深度神经网络建模攻击

93前沿研究3:破解逻辑锁定的人工智能方法

第10章实验

101实验一:可测试性设计

102实验二:芯片安全之逻辑锁定

103实验三:PUF芯片CRP仿真与建模攻击

104实验四:逻辑故障诊断

附录 数字电路逻辑门符号说明

参考文献

第1章概论

11集成电路

12数字集成电路

121组合逻辑电路

122时序逻辑电路

13芯片产业

131CMOS制造工艺

132连线

133封装

14芯片测试

15电子设计自动化

151电子设计自动化与电子设计自动化软件

152电子设计自动化软件的应用与研发

16芯片安全

161硬件安全

162芯片供应链安全

163芯片安全的挑战

164网络空间中的芯片安全

17测试与安全

171芯片测试从理论和技术上支持芯片安全

172芯片安全促进测试

18习题

第2章数字芯片故障模型

21物理缺陷与故障模型

22数字电路故障模型

221固定型故障模型

222晶体管闭合与开路故障模型

223桥接型故障模型

224输入模式故障模型

23故障等价与压缩

24案例:故障压缩

25习题

第3章数字芯片测试与故障仿真

31测试矢量生成

32组合逻辑电路测试矢量生成

321随机测试矢量生成

322穷尽测试

323D运算和D算法

324PODEM

325FAN

33时序逻辑电路测试矢量生成

331时间帧展开

332基于仿真的方法

34可测试性度量

341SCOAP

342COP

343高层次可测试性度量

35故障仿真与诊断

351串行故障仿真

352并行故障仿真

353并行矢量故障仿真

354推演故障仿真

355并发故障仿真

356差分故障仿真

36故障诊断

37故障元胞

38案例:测试矢量生成

39习题

第4章数字芯片可测试性设计

41扫描设计

411扫描单元

412扫描设计的流程

413扫描设计的测试

414扫描设计的测试矢量生成

42内建自测试

421测量矢量生成

422输出响应分析

423BIST设计规则

424BIST架构

43边界扫描

431测试访问端口

432TAP控制器

433寄存器和指令译码器

434指令

44习题

第5章其他数字芯片关键测试技术

51存储器测试

511存储器与测试之间的联系

512存储器故障

513存储器测试方法

52IDDQ测试

521IDDQ测试原理

522IDDQ测试方法

523适用故障范围

53时延测试

531延迟故障模型

532时延测试方法

54习题

第6章硬件攻击与芯片安全

61芯片供应链安全

611芯片供应链

612安全隐患及对策

62硬件IP设计与安全

621硬件IP分类

622安全隐患

63侧信道攻击

631侧信道攻击分类

632攻击方法

64面向测试的攻击

641基于扫描的攻击

642基于JTAG标准的攻击

65硬件木马

651硬件木马结构

652硬件木马分类

653防御措施

66其他物理攻击

661逆向工程

662探测攻击

663PCB攻击

67习题

第7章数字芯片的安全增强技术

71硬件混淆概述

711硬件混淆的目的

712不同层级的混淆

72混淆技术

73逻辑锁定

731设计方法

732攻击方法

74习题

第8章物理不可克隆安全芯片

81硬件安全原语

811物理不可克隆函数

812真随机数生成器

813防伪设计

82PUF的种类与应用

821PUF的分类

822PUF的评估指标

823设备认证

824密钥生成

83PUF设计

831仲裁器PUF

832异或APUF

833插入式PUF

834多路选线器PUF

835轻量级安全PUF

836前馈仲裁器PUF

837环形振荡器PUF

838双稳态环PUF

839静态随机存储器PUF

8310蝴蝶PUF

84面向PUF的攻击方法

841物理攻击方法

842建模攻击方法

843抵御建模攻击的手段

85面向PUF的可靠性攻防分析

86案例:基于FPGA的双稳态PUF硬件设计

87习题

第9章人工智能时代的数字芯片测试与安全

91前沿研究1:机器学习助力芯片测试与诊断

92前沿研究2:面向PUF的人工智能建模攻击

921基于CP分解的张量神经网络攻击

922基于神经网络计算图的近似建模攻击

923基于深度神经网络的建模攻击

924结合侧信道信息的深度神经网络建模攻击

93前沿研究3:破解逻辑锁定的人工智能方法

第10章实验

101实验一:可测试性设计

102实验二:芯片安全之逻辑锁定

103实验三:PUF芯片CRP仿真与建模攻击

104实验四:逻辑故障诊断

附录 数字电路逻辑门符号说明

参考文献

本书是根据网络空间安全(简称网安)与信息安全(简称信安)专业本科生培养计划,专为“芯片测试与硬件安全”专业课程设计的教材。该课程立足于网安、信安专业的特点,结合现有本科生培养体系,并借鉴国内外一流高校网络安全研究中心的成功经验,旨在填补电子设计自动化(EDA)研发领域的人才空白,推动芯片安全技术的教育与人才培养。本书紧密围绕网络空间安全的新兴学科,系统介绍芯片测试与硬件安全的核心技术,充分考虑读者知识背景、前置课程体系和学科基础。本书是一本不一样的“硬件”类教材:在传统“软件”类课程知识的基础上,深度融合了计算机算法分析与设计、人工智能、面向对象程序设计等内容,推动学生掌握芯片测试与安全技术的同时,也培养其跨学科的创新能力和实践能力。

第1章为概论,第2~5章介绍了故障模型、测试矢量生成、测试压缩、可测试性设计、内建自测试、故障诊断、存储器测试与时延测试等测试技术,第6~8章介绍了硬件攻击、逻辑锁定等芯片安全增强技术,以及物理不可克隆安全芯片攻防设计等,第9章讲述了利用人工智能提升芯片测试效能与安全性的若干代表性工作并展望未来的技术发展趋势,第10章配有EDA测试与安全实验,为读者提供动手实践机会。本书作为教材使用,章后附有习题。第10章中的实验脚本与样例可登录https://githubcom/TechnologyAiGroup/book1下载。建议授课学时为40小时,实验学时8小时,并要求先学习Verilog HDL语言、Python(或MATLAB)语言。

本书的特色与创新如下。

门槛适中:立足本科生课程体系,仅要求学习过“高等工程数学”和“数字电路与逻辑设计”,内容精简易学,相较国外教材更贴近国内教学需求。

重点聚焦:削弱物理层面及模拟、射频内容,专注数字集成电路,结合逻辑设计、人工智能应用及算法培养EDA领域基础技能。

实践导向:设计软件仿真与硬件实验环节,为有兴趣的学生提供实践机会,增强动手能力。

内容前沿:融入国际顶级期刊和会议研究论文与课题组多年成果,涵盖芯片测试与安全的最新技术趋势,摒弃陈旧内容,体现领域科技热点。

广泛交流:编写过程中与海内外一流高校、科研机构、晶圆代工厂及EDA企业深入沟通,确保内容兼具理论深度与产业应用价值。

通过学习,希望激发读者对芯片安全、数字集成电路产业、自主EDA技术研发的从业兴趣,掌握基本的数字芯片测试技术、数字芯片安全系统设计与攻击防御,对半导体产业链安全有整体上的框架认识。编者希望能够激发未来期望从事芯片研发的有志青年的使命感,希望他们能够为“中国芯”的崛起和发展做出贡献。

鉴于现在国际学术和工程上的普遍用法,书中数字电路符号沿用美国电气电子工程师学会标准。

参加本书编写工作的还有华中科技大学芯片测试与安全课题组的罗陈亮、皇甫璟轩、万才学等研究生同学。本书的顺利出版,要感谢华中科技大学网络空间安全学院的领导和老师的大力支持。感谢机械工业出版社编辑的宝贵意见。本书部分工作得到了国家自然科学基金(项目号62172173、62372198)资助。

由于时间仓促,书中难免存在不妥之处,敬请读者原谅,并提出宝贵意见。

第1章为概论,第2~5章介绍了故障模型、测试矢量生成、测试压缩、可测试性设计、内建自测试、故障诊断、存储器测试与时延测试等测试技术,第6~8章介绍了硬件攻击、逻辑锁定等芯片安全增强技术,以及物理不可克隆安全芯片攻防设计等,第9章讲述了利用人工智能提升芯片测试效能与安全性的若干代表性工作并展望未来的技术发展趋势,第10章配有EDA测试与安全实验,为读者提供动手实践机会。本书作为教材使用,章后附有习题。第10章中的实验脚本与样例可登录https://githubcom/TechnologyAiGroup/book1下载。建议授课学时为40小时,实验学时8小时,并要求先学习Verilog HDL语言、Python(或MATLAB)语言。

本书的特色与创新如下。

门槛适中:立足本科生课程体系,仅要求学习过“高等工程数学”和“数字电路与逻辑设计”,内容精简易学,相较国外教材更贴近国内教学需求。

重点聚焦:削弱物理层面及模拟、射频内容,专注数字集成电路,结合逻辑设计、人工智能应用及算法培养EDA领域基础技能。

实践导向:设计软件仿真与硬件实验环节,为有兴趣的学生提供实践机会,增强动手能力。

内容前沿:融入国际顶级期刊和会议研究论文与课题组多年成果,涵盖芯片测试与安全的最新技术趋势,摒弃陈旧内容,体现领域科技热点。

广泛交流:编写过程中与海内外一流高校、科研机构、晶圆代工厂及EDA企业深入沟通,确保内容兼具理论深度与产业应用价值。

通过学习,希望激发读者对芯片安全、数字集成电路产业、自主EDA技术研发的从业兴趣,掌握基本的数字芯片测试技术、数字芯片安全系统设计与攻击防御,对半导体产业链安全有整体上的框架认识。编者希望能够激发未来期望从事芯片研发的有志青年的使命感,希望他们能够为“中国芯”的崛起和发展做出贡献。

鉴于现在国际学术和工程上的普遍用法,书中数字电路符号沿用美国电气电子工程师学会标准。

参加本书编写工作的还有华中科技大学芯片测试与安全课题组的罗陈亮、皇甫璟轩、万才学等研究生同学。本书的顺利出版,要感谢华中科技大学网络空间安全学院的领导和老师的大力支持。感谢机械工业出版社编辑的宝贵意见。本书部分工作得到了国家自然科学基金(项目号62172173、62372198)资助。

由于时间仓促,书中难免存在不妥之处,敬请读者原谅,并提出宝贵意见。

- 金粉商城 (微信公众号认证)

- 金粉商城由金属加工杂志社创办。《金属加工》(原名《机械工人》),创刊于1950年,距今已经有70年历史,是面向金属加工工艺及装备领域的专业期刊。金粉商城目前经营工业类专业图书。

- 扫描二维码,访问我们的微信店铺

- 随时随地的购物、客服咨询、查询订单和物流...