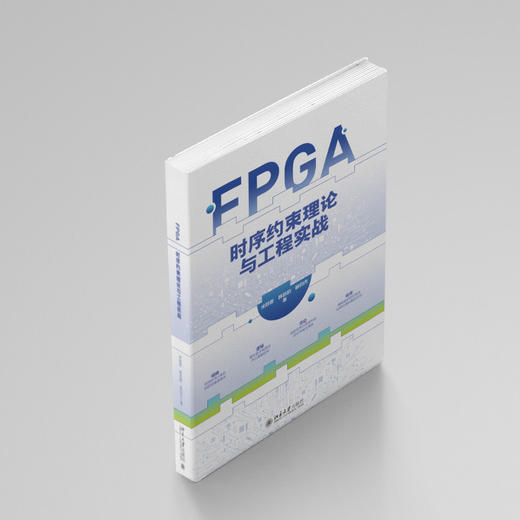

商品详情

时序分析与约束是FPGA设计中的;交通规则。

FPGA中具有丰富的触发器和布线资源,如果没有时序约束的引导,FPGA将无法

识别信号的时序关系,从而导致时序紊乱、路径拥塞、无法高速运行,甚至出现数据

传输错误。时序分析与约束的作用就是确定FPGA信号的延迟关系,以及如何通过布

局布线来优化时序电路。合理的时序设计不仅能有效规避信号延迟、时序冲突等问题,

而且能提升系统的整体性能和响应速度。

通过合理设置时钟周期、输入/输出延迟、时序例外等约束,并分析验证信号传

输路径的延迟是否满足触发器在时钟有效边沿上的建立时间(Setup Time)和保持时间

(Hold Time)的要求,可以确保数据在时钟边沿被稳定采样,不当的约束设置可能导

致时序违例(如引发亚稳态),使系统无法正常工作。因此,深入理解FPGA的时序特

性并掌握其设计原则,对于工程师和研究人员来说至关重要。

笔者在FPGA开发领域深耕十余年,创立了米联客信息科技有限公司和南京威焅

机器人科技有限公司,专注于FPGA/SoC硬件开发及国产FPGA的研发和应用。在长

期项目实践中,笔者发现FPGA时序分析与约束工作往往需要反复查阅厂商技术文档,

效率低下且耗费精力。基于这一行业痛点,笔者决定系统梳理多年积累的时序约束设

计经验,结合常见时序模型,将实践知识整理成书。

本书旨在为FPGA研发工程师提供一本实用性强、可直接参考的指南,帮助读者

快速掌握时序约束与优化的核心技能,提高在实际项目中的工作效率。

通过本书,工程师能够更高效地完成时序约束设计,减少重复查阅文档的时间消

耗,将更多精力投入创新性的研发工作中。

1.系统讲解:从时钟、触发器基础,到STA、时序路径模型,构建完整知识体系。

2.实战为王:详解RGMII、ADC/DAC、SPI、I2C等常用接口的完整约束实例,即学即用,一步步教你写出可靠时序。

3.通俗易懂:从基础概念到高级约束,辅以丰富图表与分析,适合初学者与进阶开发者。

4.问题导向:聚焦如何有效避免时序违例,不止讲语法,更教授分析方法论,直接解决工程设计的核心痛点。

5.学习资源:提供实战案例代码、视频课程、教学PPT等实用学习资源。

本书系统阐述现场可编程门阵列(Field Programmable Gate Array,FPGA)设计中的时序分析与约束技术,从时序约束的基本概念讲起,逐步深入到不同时序模型的约束方法,并结合实战案例,带领读者掌握核心技能,有效避免设计中的时序违例。

全书共14章,内容覆盖时钟与触发器特性、静态时序分析、建立/保持时间与时间裕量、时序路径模型等基础 知识;进而详细讲解主时钟、生成时钟、虚拟时钟、输入/输出延时、伪路径、多周期路径、最大最小延迟等关键约 束语法与设置,并介绍FPGA代码设计中的时序收敛方法。为强化实战,书中提供了丰富的案例,包括常用的精简 千兆介质无关接口(RGMII)、模数转换器(ADC)/数模转换器(DAC)、串行外设接口(SPI)、内部集成电路(I2C)接口等约束实例。

本书内容通俗易懂,案例丰富,实用性强,不仅非常适合FPGA初学者、进阶开发者,以及对时序分析感兴趣的技术爱好者阅读,也可作为相关领域理想的培训教材。

米联客,专注于FPGA/系统级芯片(SoC)硬件开发和软件生态建设,致力于为中国工程师提供技术基座生态支持,以FPGA技术为核心,构建开放共享的研发生态,通过技术交流、项目协作和社区支持,赋能工程师高效创新、降低成本,助力中国科技领域突破与产业化落地。

韩歆韵,米联客资深FPGA课程讲师,专注于FPGA领域的教学内容研发,负责文档教程的编写与视频课程的录制,已推出基础篇、时序篇、UDP篇三大核心模块,内容覆盖从入门到进阶的关键技术点。

杨钧杰,米联客资深FPGA逻辑工程师,熟练使用安路、Xilinx等开发平台,负责通信类产品及解决方案的整体设计与实现,主导开发了40G/100G UDP协议栈、10G TCP协议栈以及光纤相机方案等关键技术,拥有丰富的高速接口设计经验。

时序约束与设计实战

第1章 时序约束概述

1.1 什么是时序约束 002

1.2 时序约束的影响 003

1.3 如何学习时序约束 004

1.3.1 时序约束的基本概念005

1.3.2 时序约束方法005

1.3.3 FPGA代码设计中的时序收敛方法006

1.4 总结 007

第2章 时序约束基础

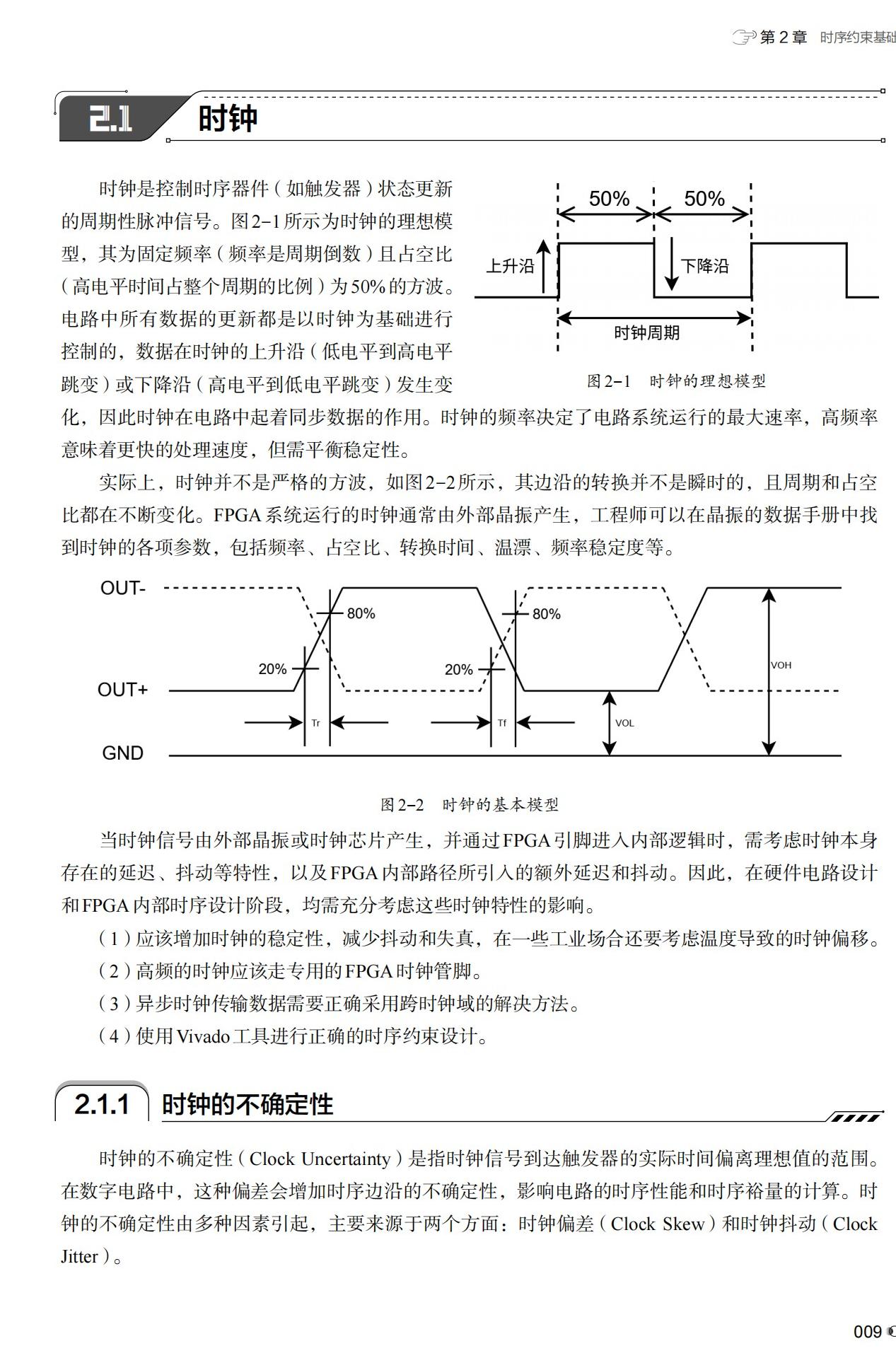

2.1 时钟 009

2.1.1 时钟的不确定性009

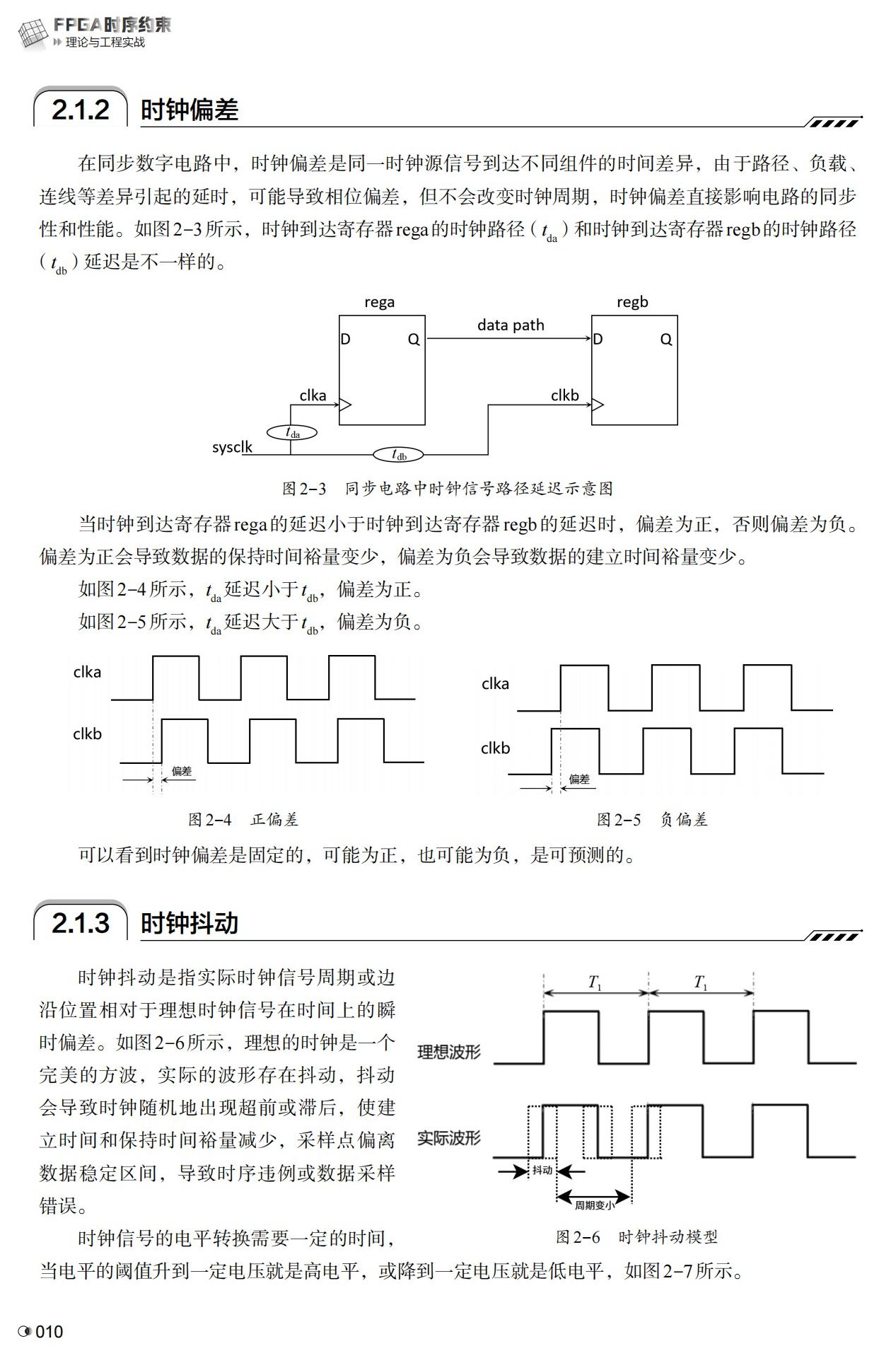

2.1.2 时钟偏差010

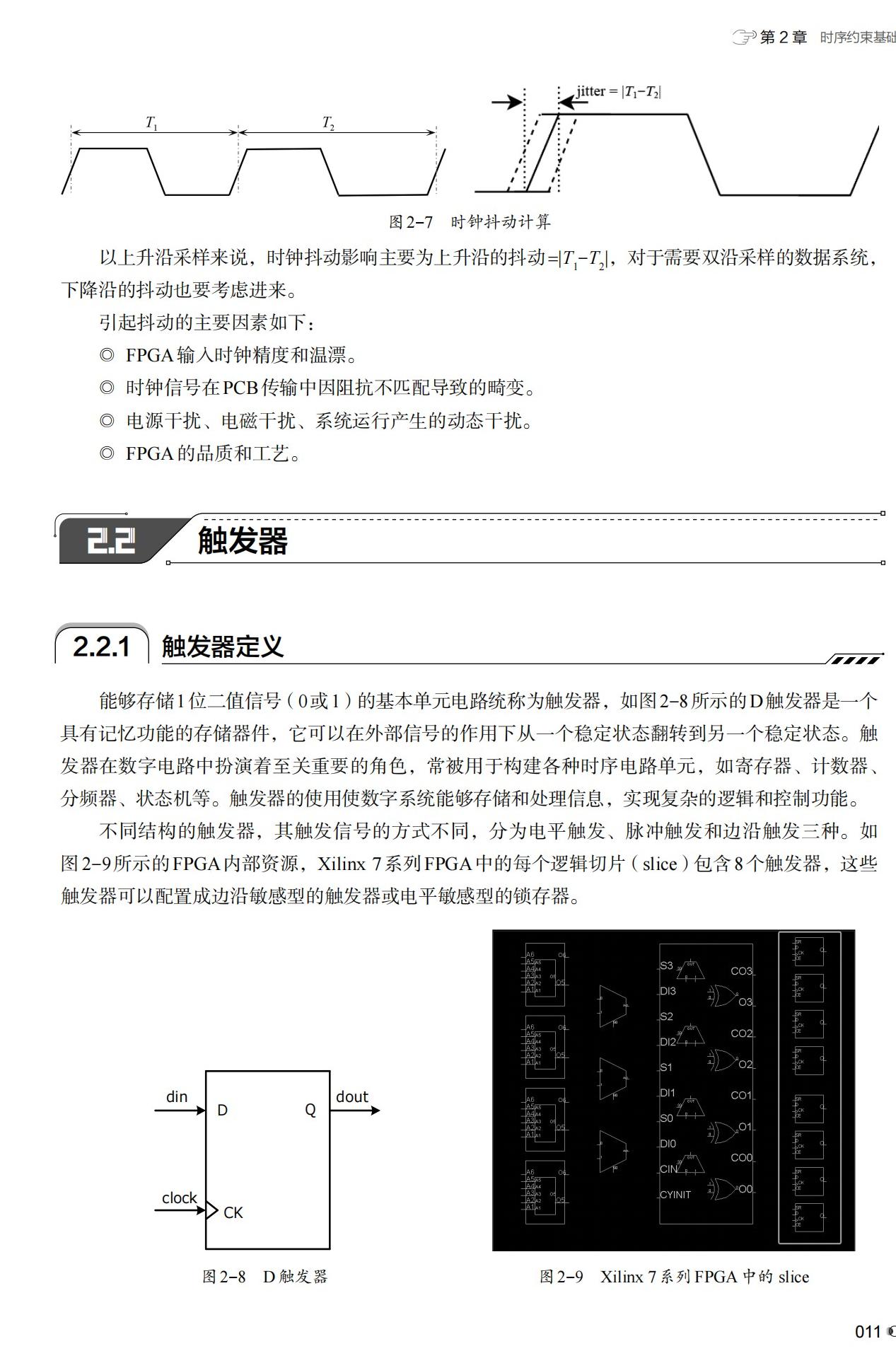

2.1.3 时钟抖动010

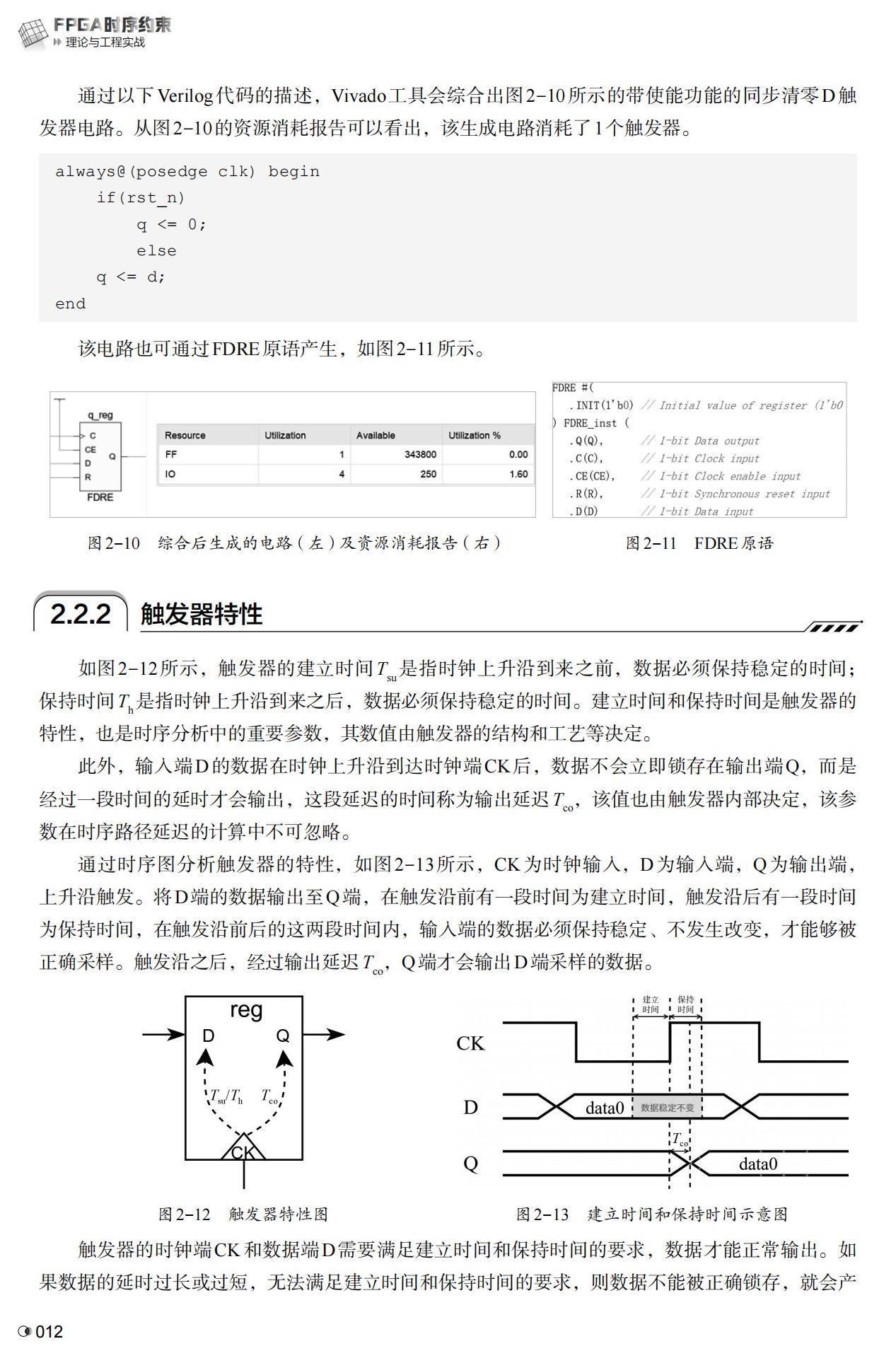

2.2 触发器011

2.2.1 触发器定义011

2.2.2 触发器特性012

2.3 静态时序分析概念013

2.4 时序路径模型014

2.5 数据到达路径和数据需求路径015

2.6 发射沿和锁存沿016

2.7 建立时间和保持时间的关系016

2.8 建立时间裕量和保持时间裕量017

2.9 总结017

第3章 时钟约束

3.1 主时钟约束020

3.2 生成时钟约束021

3.3 虚拟时钟约束023

3.3.1 虚拟时钟和物理时钟的比较024

3.3.2 虚拟时钟的应用场景025

3.4 时钟特性约束027

3.4.1 用户时钟不确定性027

3.4.2 时钟延时027

3.5 总结028

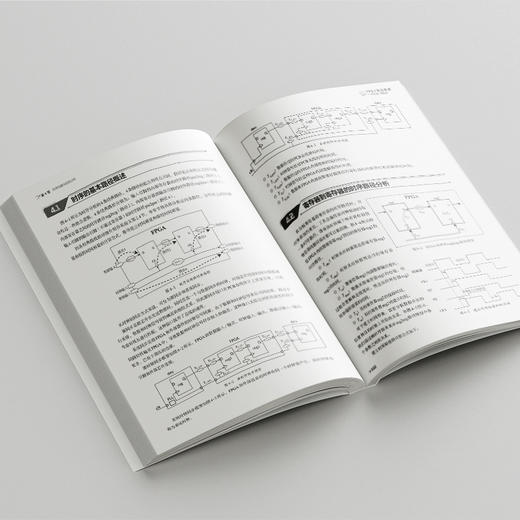

第4章 时序的基本路径分析

4.1 时序的基本路径概述031

4.2 寄存器到寄存器的时序路径分析032

4.3 输入延迟时序路径分析034

4.3.1 系统同步分析034

4.3.2 源同步分析036

4.4 输出延迟时序路径分析038

4.4.1 系统同步分析038

4.4.2 源同步分析039

4.5 引脚到引脚的时序路径分析041

4.6 总结042

第5章 输入延迟约束

5.1 系统同步输入约束044

5.1.1 系统同步接口单沿采样044

5.1.2 系统同步接口双沿采样046

5.2 源同步输入约束047

5.2.1 源同步接口单沿采样中心对齐047

5.2.2 源同步接口双沿采样中心对齐049

5.2.3 源同步接口单沿采样边沿对齐050

5.2.4 源同步接口双沿采样边沿对齐053

5.3 总结055

第6章 输出延迟约束

6.1 系统同步输出约束057

6.1.1 系统同步接口单沿采样057

6.1.2 系统同步接口双沿采样059

6.2 源同步输出约束060

6.2.1 源同步接口单沿采样060

6.2.2 源同步接口双沿采样063

6.3 总结065

第7章 时序例外约束

7.1 伪路径约束067

7.2 多周期约束068

7.2.1 End Multicycle Setup069

7.2.2 Start Multicycle Setup069

7.2.3 Start Multicycle Hold070

7.2.4 End Multicycle Hold071

7.2.5 同频同相的多周期约束071

7.2.6 同频不同相的多周期约束073

7.2.7 快时钟域到慢时钟域的多周期约束074

7.2.8 慢时钟域到快时钟域的多周期约束076

7.3 最大最小延迟约束077

7.4 总结078

第8章 FPGA代码设计中的时序收敛方法

8.1 复位电路设计080

8.1.1 同步复位080

8.1.2 异步复位081

8.1.3 异步复位同步释放082

8.2 跨时钟域设计084

8.2.1 单比特信号跨时钟域085

8.2.2 多比特信号跨时钟域088

8.3 代码模块的拆分089

8.4 时钟组090

8.5 总结091

第9章 时序分析和时序约束演练

9.1 时序分析工具的使用093

9.1.1 添加约束093

9.1.2 查看时序报告099

9.2 内部路径时序报告分析104

9.2.1 路径分析104

9.2.2 片内资源时序优化107

9.3 输入延迟时序优化112

9.3.1 时钟直接输入的情况114

9.3.2 时钟经过PLL的情况118

9.4 输出延迟时序优化129

9.4.1 随路时钟选择132

9.4.2 输出延迟时序违例解决办法136

9.4.3 输出延迟和输入延迟的区分137

9.5 总结138

第10章 千兆以太网RGMII约束实例

10.1 RGMII140

10.1.1 RGMII信号定义140

10.1.2 RGMII信号组合定义141

10.1.3 RGMII的三种速率模式142

10.2 RGMII时序142

10.2.1 发送端143

10.2.2 接收端143

10.2.3 B50610 RGMII PHY144

10.2.4 88E1518 RGMII PHY141

10.2.5 RTL8211 RGMII PHY146

10.2.6 YT8531(D)C RGMII接口 PHY148

10.3 RGMII时序约束149

10.3.1 RX接口延时模式约束149

10.3.2 RX接口非延时模式约束153

10.3.3 TX接口延时模式约束160

10.3.4 TX接口非延时模式约束165

10.4 总结168

第11章 ADS422x接口约束实例

11.1 125 MHz时钟采样的情况172

11.2 250 MHz时钟采样的情况175

11.3 总结178

第12章 AD9248/AD9767接口约束实例

12.1 AD9248181

12.2 AD9767191

12.3 总结198

第13章 SPI AD7606约束实例

13.1 AD7606201

13.2 总结208

第14章 EEPROM I2C总线约束实例

14.1 M24C02211

14.2 总结218

- 新华一城书集 (微信公众号认证)

- 上海新华书店官方微信书店

- 扫描二维码,访问我们的微信店铺

- 随时随地的购物、客服咨询、查询订单和物流...