商品详情

书名:可测性设计与智能故障诊断

定价:69.0

ISBN:9787111710035

作者:林海军

本书主要从理论和应用方法两个方面对可测性设计与智能故障诊断进行研究,全书共9章,分别介绍了可测性设计和故障诊断的发展,基于沃尔泰拉核的非线性电路智能诊断以及测试激励优化和特征选择与提取,基于维纳核的非线性模拟电路故障诊断,模拟电路智能故障诊断系统设计,MIMO非线性系统的建模及故障诊断,基于信息融合技术的电路故障诊断,数字电路的可测性设计,以及混合电路的可测性设计。各章还给出了电路的参数建模和非参数建模的方法,并提供了范例,以期协助读者解决非线性电路故障诊断问题,提高诊断的准确率和效率。

本书适合从事虚拟仪器、电路设计,特别是从事集成电路故障诊断和可测性设计的研究人员阅读参考。

前言

第1章绪论

1.1可测性设计的起源与发展

1.2可测性设计的相关标准及方法

1.2.1可测性设计的相关标准

1.2.2可测性设计的方法

1.3电路的故障与诊断

1.3.1电路故障的分类

1.3.2数字电路的故障诊断方法

1.3.3模拟电路的故障诊断方法

1.4电路故障诊断的研究状况与发展趋势

1.4.1国外电路故障诊断的研究状况

1.4.2我国电路故障诊断的研究状况

1.4.3电路故障诊断发展趋势

第2章基于沃尔泰拉核的非线性电路智能诊断

2.1引言

2.2非线性模拟电路沃尔泰拉级数描述

2.3非线性模拟电路离散沃尔泰拉核的测量

2.3.1连续系统沃尔泰拉核的获取

2.3.2离散系统频域模型

2.3.3频域分离技术和测试频率选择

2.3.4快速多点法频域核的测量

2.4基于沃尔泰拉核及神经网络的智能故障诊断

2.4.1基于沃尔泰拉核的智能诊断原理及步骤

2.4.2标准BP算法的基本原理

2.4.3BP算法神经网络设计

2.5本章小结

第3章基于沃尔泰拉核诊断的测试激励优化及特征选择与提取

3.1引言

3.2退火遗传混合优化算法研究

3.2.1遗传算法的抗早熟改进

3.2.2模拟退火算法的收敛速度改进

3.2.3改进的退火遗传混合优化算法(MSAGA)

3.3退火遗传混合测试激励优化方法

3.3.1退火遗传混合激励优化流程

3.3.2目标函数的构造

3.3.3降温策略

3.3.4测试激励优化实例

3.4故障特征的智能选择与提取方法研究

3.4.1退火遗传特征选择方法

3.4.2退火遗传特征提取方法

3.4.3基于退火遗传的沃尔泰拉核特征选择和提取

3.4.4沃尔泰拉核的退火遗传特征选择实例

3.5本章小结

第4章基于维纳核的非线性模拟电路故障诊断

4.1引言

4.2非线性模拟电路的维纳级数描述

4.3维纳核的获取

4.3.1离散维纳核的获取方法

4.3.2维纳核的间接获取方法研究

4.4维纳核的退火遗传特征选择和提取方法

4.4.1基于MSAGA的维纳核的特征选择和提取方法

4.4.2维纳核的退火遗传特征选择实例

4.5基于维纳核及神经网络的故障诊断研究

4.6诊断实例

4.7本章小结

第5章模拟电路智能故障诊断系统设计

5.1引言

5.2模拟电路智能故障诊断系统原理及总体结构

5.2.1系统的原理

5.2.2系统的总体结构

5.3智能诊断系统设计

5.3.1示波器功能单元设计

5.3.2高斯白噪声发生单元设计

5.3.3信源/采集器单元设计

5.3.4智能诊断系统软件设计

5.4非线性电路智能故障诊断系统诊断实例

5.5本章小结

第6章MIMO非线性系统的建模及故障诊断

6.1引言

6.2MIMO非线性电路的沃尔泰拉核建模

6.2.1MIMO的沃尔泰拉级数描述

6.2.2MIMO非线性模拟电路GFRF的参数辨识

6.2.3MIMO非线性模拟电路GFRF的非参数辨识

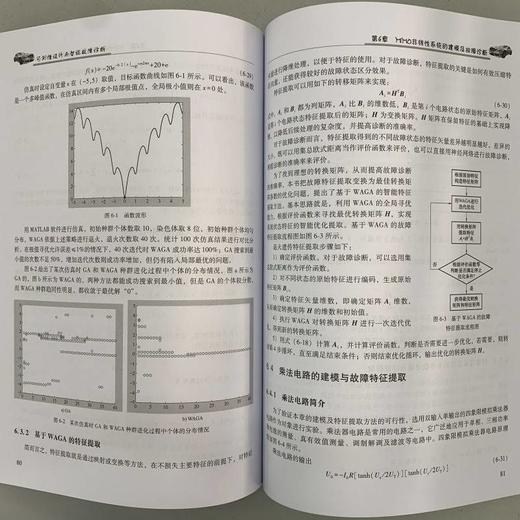

6.3基于整体退火遗传的特征提取

6.3.1整体退火遗传算法

6.3.2基于WAGA的特征提取

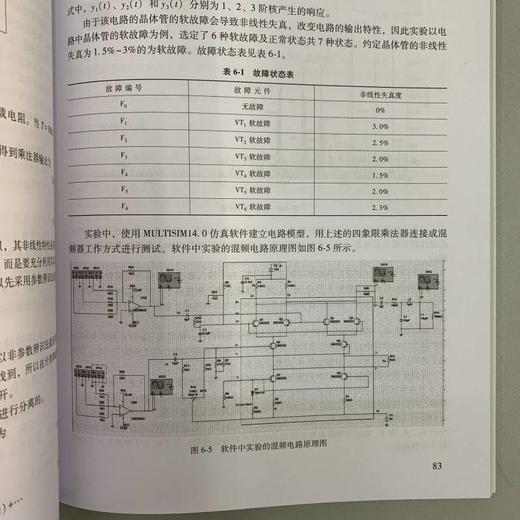

6.4乘法电路的建模与故障特征提取

6.4.1乘法电路简介

6.4.2四象限乘法器的非参数建模及特征提取

6.5本章小结

第7章基于信息融合技术的电路故障诊断

7.1引言

7.2信息融合技术的起源与发展

7.3信息融合层次分类及过程

7.3.1依据抽象程度的信息融合层次分类

7.3.2依据I/O特征的信息融合层次分类

7.3.3信息融合的过程

7.4信息融合方法

7.4.1贝叶斯估计法

7.4.2卡尔曼滤波法

7.4.3证据组合法

7.4.4概率统计方法

7.4.5D-S证据推理方法

7.4.6人工神经网络法

7.5基于信息融合的电路故障诊断方法

7.6非线性模拟电路多软故障的信息融合诊断

7.6.1基于双维纳核信息融合的智能故障诊断

7.6.2维纳核的获取

7.6.3双核特征的智能优化融合选择提取

7.6.4神经网络设计和训练

7.6.5故障诊断实例

7.7本章小结

第8章数字电路的可测性设计

8.1可测性设计研究背景

8.2数字电路可测性设计方法

8.2.1全扫描技术

8.2.2部分扫描技术

8.3边界扫描

8.3.1边界扫描技术原理

8.3.2TAP控制器

8.3.3测试数据寄存器

8.3.4指令寄存器和边界扫描测试指令集

8.3.5边界扫描描述语言

8.3.6边界扫描测试的总线配置方式

8.3.7数字电路的边界扫描测试设计方法

8.4数字电路边界扫描系统示例

8.4.1边界扫描系统的JTAG控制器开发

8.4.2互联测试和功能测试

8.5本章小结

第9章混合电路的可测性设计

9.1IEEE 1149.4标准要点剖析

9.1.1混合电路边界扫描的基本原理

9.1.2元件的基本结构

9.1.3模拟边界模块

9.1.4测试总线接口电路(TBIC)

9.1.5模拟边界扫描指令剖析

9.2混合边界扫描主要的测试形式

9.2.1完备性测试

9.2.2功能测试

9.2.3互连测试

9.2.4簇测试

9.3混合边界扫描测试系统设计

9.3.1混合边界扫描测试系统的总体结构

9.3.2混合边界扫描测试系统的设计简介

9.3.3混合边界扫描测试的工作过程

9.4基于边界扫描的模拟电路板级可测性设计

9.4.1STA400内核工作原理简介

9.4.2STA400在模拟电路可测性设计中的应用

9.5本章小结

参考文献

- 机械工业出版社旗舰店 (微信公众号认证)

- 扫描二维码,访问我们的微信店铺

- 随时随地的购物、客服咨询、查询订单和物流...