半导体工艺可靠性 甘正浩 黄威森 刘俊杰 半导体与集成电路关键技术丛书 微电子 集成电路 半导体工艺技术书籍

| 运费: | 免运费 |

商品详情

书名:半导体工艺可靠性

定价:199.0

ISBN:9787111764946

作者:[中]甘正浩(Zhenghao Gan) [美]黄威森(Waisum Wong)

内容提要:

半导体制造作为微电子与集成电路行业中非常重要的环节,其工艺可靠性是决定芯片性能的关键。本书详细描述和分析了半导体器件制造中的可靠性和认定,并讨论了基本的物理和理论。本书涵盖了初始规范定义、测试结构设计、测试结构数据分析,以及工艺的最终认定,是一本实用的、全面的指南,提供了验证前端器件和后端互连的测试结构设计的实际范例。

本书适合从事半导体制造及可靠性方面的工程师与研究人员阅读,也可作为高等院校微电子等相关专业高年级本科生和研究生的教材和参考书。

目录:

译者序

第1部分概述

第1章引言3

1.1背景3

1.2工艺可靠性项4

1.2.1FEOL4

1.2.2BEOL6

1.3工艺相关的可靠性8

1.4可靠性评估方法9

1.5本书的组织结构10

参考文献11

第2章器件物理基础14

2.1基本材料特性介绍14

2.1.1导体、半导体和绝缘体14

2.1.2电子和空穴能量16

2.1.3半导体中的碰撞与能量交换17

2.2PN结18

2.2.1PN结能带18

2.2.2PN结偏置19

2.2.3结电容20

2.3金属-氧化物-半导体电容的物理基础21

2.3.1金属-氧化物-半导体电容的能带21

2.3.2金属-氧化物-半导体电容的电容-电压曲线23

2.4金属-氧化物-半导体场效应晶体管物理特性24

2.4.1金属-氧化物-半导体场效应晶体管的电流-电压特性24

2.4.2长沟道金属-氧化物-半导体场效应晶体管的Vt27

2.4.3金属-氧化物-半导体场效应晶体管中的电容27

2.5金属-氧化物-半导体场效应晶体管的二阶效应29

2.5.1短沟道效应29

2.5.2宽度效应30

2.5.3栅致漏极泄漏电流31

2.5.4硼渗透32

2.5.5衬底偏置的影响33

2.6界面陷阱和氧化层陷阱33

参考文献36

第3章金属-氧化物-半导体制造工艺流程37

3.1前道工艺37

3.2Cu双大马士革后端工艺42

参考文献46

第4章可用于器件可靠性表征的测量48

4.1电容-电压测量48

4.2直流电流-电压49

4.2.1从直流电流-电压测量中提取界面陷阱52

4.2.2从直流电流-电压测量中提取氧化层陷阱54

4.3栅控二极管方法55

4.4电荷泵测量57

4.5用于界面和氧化层陷阱分离的中间带隙测量60

4.6载流子分离测量61

4.7电流-电压特性62

参考文献63

第2部分前道工艺(FEOL)

第5章热载流子注入67

5.1最大沟道电场69

5.2HCI的物理机制71

5.2.1电场驱动的CHC机制71

5.2.2能量驱动的沟道-热载流子机制:电子-电子散射73

5.2.3多重振动激发机制74

5.2.4NMOS热载流子注入机理/模型75

5.2.5PMOS热载流子注入机理/模型76

5.3热载流子注入表征方法77

5.3.1监控的器件参数77

5.3.2热载流子注入退化模型78

5.3.3寿命外推80

5.4对热载流子注入屏蔽效应的表征82

5.5热载流子注入退化饱和83

5.6温度对热载流子注入的影响84

5.7体偏置对热载流子注入的影响85

5.8结构对热载流子注入的影响85

5.8.1沟道宽度对热载流子注入的影响85

5.8.2沟道长度对热载流子注入的影响89

5.8.3补偿侧墙对热载流子注入的影响91

5.8.4栅极边缘与浅沟槽隔离边缘间距的影响94

5.9工艺对热载流子注入性能的影响95

5.9.1漏区工程95

5.9.2栅极氧化层的鲁棒性96

5.10热载流子注入认定实践100

参考文献101

第6章栅极氧化层完整性和时间相关的介质击穿108

6.1金属-氧化物-半导体结构的隧穿108

6.1.1栅极泄漏隧穿机制108

6.1.2依赖极性的Qbd和Tbd114

6.1.3栅极泄漏电流与Vbd/Tbd的关系117

6.2栅极氧化层介质击穿机理120

6.2.1本征与非本征击穿120

6.2.2随时间变化的介质击穿122

6.2.3Vbd与Tbd的相关性123

6.2.4缺陷产生模型124

6.2.5软击穿129

6.3应力诱导的泄漏电流131

6.4栅极氧化层完整性测试结构和失效分析132

6.4.1体结构132

6.4.2多晶硅边缘密集结构132

6.4.3浅沟槽-隔离-边缘密集结构133

6.4.4浅沟槽隔离拐角密集结构134

6.4.5栅极氧化层完整性失效分析135

6.5栅极氧化层时间相关介质击穿模型,寿命外推法135

6.5.1Weibull分布135

6.5.2活化能135

6.5.31/E模型、E模型、V模型和幂律模型136

6.5.4面积按比例变化140

6.6工艺对栅极氧化层完整性和时间变化的介质击穿改进的影响140

6.6.1氧化层厚度的影响140

6.6.2氮化的影响140

6.6.3氢/D2的影响142

6.6.4金属污染143

6.6.5多晶硅晶粒结构的影响144

6.6.6多晶硅剖面的影响(多晶硅基脚)145

6.6.7栅极氧化层预清洗和刻蚀的影响145

6.6.8牺牲氧化后退火环境的影响145

6.6.9无牺牲氧化层效应148

6.6.10光刻胶附着力的影响150

6.6.11铟注入的影响151

6.6.12幂律模型指数的工艺因子151

6.7工艺认定实践155

参考文献156

第7章负偏置温度不稳定性162

7.1负偏置温度不稳定性退化机制164

7.1.1反应-扩散模型164

7.1.2恢复167

7.2退化时间指数n,活化能Ea,电压/电场加速因子γ171

7.2.1退化时间指数n171

7.2.2活化能(Ea)172

7.2.3电压/电场加速因子γ173

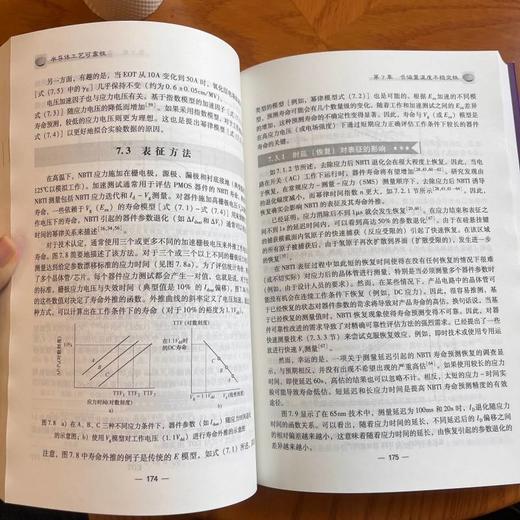

7.3表征方法174

7.3.1时延(恢复)对表征的影响175

7.3.2应力-电压和应力-时间影响177

7.3.3不间断应力方法179

7.3.4体偏置对负偏置温度不稳定性的影响183

7.4为什么反型的PMOS最差186

7.5结构对负偏置温度不稳定性的影响188

7.5.1沟道长度依赖性189

7.5.2沟道宽度依赖性191

7.5.3栅极氧化层厚度相关性192

7.6工艺对负偏置温度不稳定性的影响194

7.6.1氮及其分布194

7.6.2氟掺入197

7.6.3栅极氧化层和Si-SiO2界面质量198

7.6.4H2/D2退火199

7.6.5后道工艺199

7.6.6等离子体诱导损伤的影响200

7.6.7硼渗透200

7.6.8接触刻蚀截止层的效果200

7.6.9Si衬底取向的影响201

7.7动态负偏置温度不稳定性202

7.8工艺认定实践202

参考文献204

第8章等离子体诱导损伤212

8.1引言212

8.2等离子体诱导损伤机制214

8.2.1等离子体密度214

8.2.2晶圆上等离子体的不均匀性214

8.2.3电子屏蔽效应215

8.2.4逆电子屏蔽效应215

8.2.5紫外线辐射216

8.3等离子体诱导损伤的表征方法217

8.4等离子体特性219

8.4.1等离子体表征方法219

8.4.2等离子体I-V特性和等离子体参数对等离子体I-V及损伤的影响220

8.5衬底对等离子体损伤的影响222

8.5.1为什么PMOS比NMOS更差222

8.5.2保护器件的作用224

8.5.3栅极氧化层厚度对等离子体损伤的影响226

8.5.4对绝缘体上硅器件的影响227

8.5.5连接到源极/漏极和衬底的天线228

8.5.6阱结构影响228

8.6结构对等离子体损伤的影响229

8.6.1天线指密度的影响230

8.6.2通过桥接设计避免等离子体诱导损伤230

8.6.3潜在的天线效应231

8.6.4扩展的天线效应232

8.6.5作为检测器的电容与晶体管233

8.7工艺对等离子体诱导损伤的影响233

8.7.1退火对栅极氧化层工艺诱导损伤的影响233

8.7.2钝化刻蚀效应235

8.7.3SiN帽层NH3等离子体预处理工艺对等离子体诱导损伤的影响235

8.7.4等离子体参数对等离子体诱导损伤的影响236

8.7.5金属前介质沉积236

8.7.6金属间刻蚀和通孔刻蚀的影响238

8.7.7工艺温度的影响238

8.7.8通过设备改造降低等离子体电荷损伤239

8.7.9等离子体诱导损伤的渐进退化特征240

8.7.10栅极氧化层的鲁棒性240

8.7.11金属间介质沉积的影响241

8.7.12阻挡层/种子层沉积的影响241

8.7.13晶圆背面绝缘层241

8.8与等离子诱导体损伤相关的其他可靠性问题241

8.8.1热载流子注入242

8.8.2负偏置温度不稳定性244

8.8.3栅极氧化层完整性244

8.9工艺认定实践245

参考文献246

第9章集成电路的静电放电保护254

9.1静电放电事件背景254

9.2静电放电保护器件的建模258

9.2.1包含寄生双极晶体管的NMOS器件的物理行为259

9.2.2静电放电紧凑模型的开发261

9.2.3在SPICE中的模型实现265

9.2.4结果与讨论267

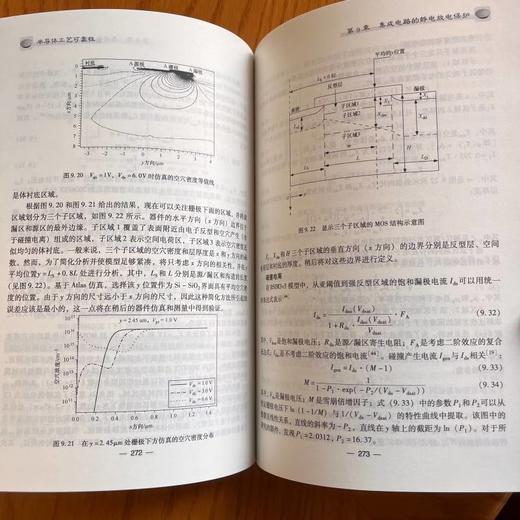

9.2.5先进的金属-氧化物-半导体模型270

9.3静电放电测量和测试285

9.3.1基于输电线路脉冲技术的静电放电测量实验装置286

9.3.2负载匹配电路的开发288

9.3.3等效于人体模型的传输线脉冲宽度的确定292

9.4片上静电放电保护方案设计301

9.4.1基于晶闸管的静电放电设计306

9.4.2基于二极管的静电放电保护设计317

9.4.3射频优化327

参考文献340

第3部分后道工艺(BEOL)

第10章电迁移347

10.1电迁移物理347

10.2电迁移表征349

10.2.1封装级可靠性与晶圆级可靠性349

10.2.2金属线测试结构349

10.2.3临界长度测试结构350

10.2.4漂移速度测试结构352

10.2.5热产生测试结构352

10.2.6涉及两层通孔的测试结构354

10.3电迁移失效时间355

10.3.1Black方程(双参数对数正态分布)355

10.3.2双峰对数正态分布357

10.3.3三参数对数正态分布359

10.4电迁移失效模式360

10.5电迁移机制的理解362

10.5.1接触点的电迁移362

10.5.2Al和W通孔的电迁移362

10.5.3Cu互连的电迁移364

10.6工艺对电迁移的影响366

10.6.1Cu/低k互连,Cu/低k界面控制366

10.6.2Cu-互连微结构的控制369

10.6.3阻挡层/种子层效应369

10.6.4溶质/掺杂对电迁移的影响374

10.6.5双大马士革结构剖面的影响374

10.6.6含氧量对Cu互连的影响375

10.6.7预先存在的孔洞对电迁移的影响377

10.7结构对电迁移的影响378

10.7.1通孔/线互连结构378

10.7.2储层效应(线延伸效应)382

10.7.3金属临界长度效应384

10.7.4金属厚度/宽度相关性385

10.8交流条件下的电迁移385

10.8.1峰值、平均和方均根电流密度的定义386

10.8.2Jrms的表征386

10.9工艺认定实践389

参考文献390

第11章应力迁移400

11.1引言400

11.2应力迁移物理基础401

11.2.1应力迁移机制的基本认识401

11.2.2活跃的扩散体积403

11.2.3孔洞成核404

11.2.4应力梯度405

11.2.5观察到应力迁移的新失效机制406

11.2.6应力诱发孔洞化的数学模型407

11.3应力迁移表征408

11.3.1应力迁移测试结构408

11.3.2应力迁移表征方法411

11.4应力迁移失效模式411

11.5应力迁移的有限元法412

11.5.1有限元方法模型描述413

11.5.2表征应力的有限元方法参数及实例416

11.6工艺对应力迁移的影响421

11.6.1通孔凿蚀效应421

11.6.2金属化层的相关性421

11.6.3阻挡层效应423

11.6.4Cu合金效应424

11.6.5介质依赖性426

11.6.6铜-微结构效应427

11.6.7淬火效应428

11.6.8镀Cu化学428

11.6.9Cu覆盖层效应428

11.6.10其他效应429

11.7应力迁移的几何效应(通过设计改善应力迁移)429

11.7.1金属板几何形状的影响429

11.7.2通孔错位的影响432

11.7.3介质槽的影响434

11.7.4双(多)通孔效应437

11.8工艺认定实践438

参考文献438

第12章金属间介质击穿446

12.1引言446

12.2测试结构和方法449

12.2.1测试结构449

12.2.2测试方法451

12.3金属间介质击穿失效机制/模式454

12.3.1失效机制454

12.3.2失效模式456

12.4寿命模型458

12.4.1Weibull分布458

12.4.21/E模型、E模型和SQRT(E)模型459

12.4.3活化能461

12.4.4面积/长度按比例变化463

12.4.5缺陷密度(DD)463

12.5影响IMD可靠性的因素464

12.5.1材料相关性464

12.5.2水分的影响466

12.5.3临界尺寸控制467

12.5.4Cu-帽层界面质量控制469

12.5.5新型帽层470

12.5.6阻挡层效应470

12.5.7自组装分子纳米层作为扩散阻挡层471

12.5.8Cu CMP效应471

12.6电压斜坡(Vbd)与时间相关的介质击穿(Tbd)的关系472

12.7与时间相关的堆叠通孔梳状结构的介质击穿特性475

12.8介质可靠性评估的有限元建模476

12.8.1电场仿真的有限元建模476

12.8.2提取低k介质材料k值的有限元模型476

12.8.3低k介质材料k值漂移的有限元模型477

12.8.4工艺诱导损伤评价的有限元模型480

12.9工艺认定实践480

参考文献482

译者序

微电子行业中的一个非常重要的环节是半导体制造,制造过程中包含了很多的工艺步骤,工艺的可靠性是决定芯片代工企业能否制造出性能优异的集成电路的关键。半导体工艺可靠性对于该领域研究的意义非常重大。本书的作者是三位来自先进芯片代工企业的一线工程师,对于工艺的可靠性给出了实用和全面的论述。

本书分为12章,包括基本器件物理学、MOS制造工艺流程、用于器件可靠性表征的测量、热载流子注入、栅极氧化层完整性 (GOI) 和时间相关的介质击穿 (TDDB)、负偏置温度不稳定性、等离子体诱导损伤、集成电路的静电放电保护、电迁移、应力迁移和金属间介质击穿。书中除了对工艺可靠性问题进行了理论的描述和分析外,同时还给出了相应测试的实际例子。本书的作者作为资深工程师,他们的丰富经验使得本书具有非常高的实用价值。因而本书对于工艺相关领域的工程师无疑是一本非常好的参考书。

本书由北方工业大学杨兵老师完成翻译和整理工作。感谢机械工业出版社编辑江婧婧为原著版权和译著出版所做的大量工作。感谢家人一如既往的理解和支持,使我能静下心来完成翻译工作。书中翻译有不妥甚至错误之处,敬请读者不辞吝教。

杨兵

2024年5月

- 机械工业出版社旗舰店 (微信公众号认证)

- 扫描二维码,访问我们的微信店铺

- 随时随地的购物、客服咨询、查询订单和物流...