商品详情

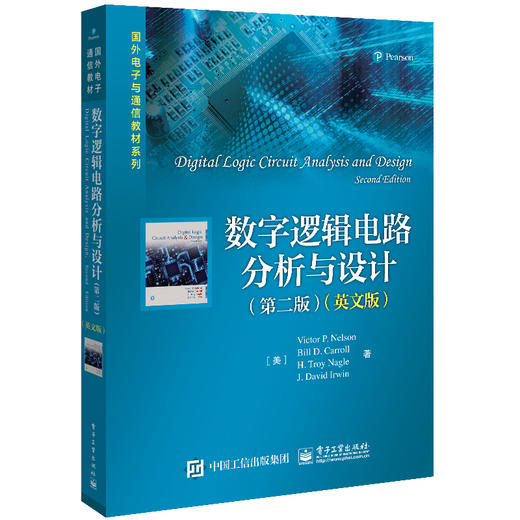

书名:数字逻辑电路分析与设计(第二版)(英文版)

定价:129.0

ISBN:9787121398704

作者:维克多·P·纳尔逊

版次:第1版

出版时间:2020-11

内容提要:

本书以介绍数字设计的基础知识以及丰富案例为主要特色,并在**版的基础上进行了全面的修订与更新,更加突出了数字设计相关技术的应用。本书内容包括:计算机与数字系统,数制系统,逻辑电路与布尔代数,组合逻辑电路分析与设计,时序逻辑电路简介,同步时序逻辑电路分析与设计,异步时序逻辑电路分析与设计,可编程逻辑器件,数字系统设计。本书对基本概念和理论的讲解具有一定的广度与深度,同时添加了非常实用的设计方法。

作者简介:

Victor P. Nelson,美国俄亥俄州立大学电气工程博士,现为奥本大学电气与计算机工程教授。IEEE计算机协会和IEEE教育协会的终身高级会员。Nelson教授出版过多部数字设计方面的教材,发表过大量的文章,并且是多家公司的微处理器应用和容错系统顾问。

Victor P. Nelson,美国俄亥俄州立大学电气工程博士,现为奥本大学电气与计算机工程教授。IEEE计算机协会和IEEE教育协会的终身高级会员。Nelson教授出版过多部数字设计方面的教材,发表过大量的文章,并且是多家公司的微处理器应用和容错系统顾问。

目录:

0 Computers and Digital Systems 1

Learning Objectives 1

0.1 A Brief History of Computing 1

0.1.1 Beginnings: Mechanical Computers 2

0.1.2 Early Electronic Computers 2

0.1.3 The First Four Generations of Computers 2

0.1.4 The Fifth Generation and Beyond 4

0.2 Digital Systems 4

0.2.1 Digital versus Analog Systems 5

0.2.2 Digital System Levels of Abstraction 5

0.3 Electronic Technologies 8

0.3.1 Moore’s “Law” 9

0.3.2 Fixed versus Programmable Logic 10

0.3.3 Microcontrollers 10

0.3.4 Design Evolution 10

0.4 Applications of Digital Systems 12

0.4.1 General-Purpose Digital Computers 12

0.4.2 Controllers 17

0.4.3 Internet of Things (IoT) 18

0.4.4 Interfacing 18

0.5 Summary and Review Questions 20

0.6 Collaboration Activities 20

References 21

1 Number Systems and Digital Codes 22

Learning Objectives 22

1.1 Number Systems 22

1.1.1 Positional and Polynomial Notations 23

1.1.2 Commonly Used Number Systems 23

1.2 Arithmetic 24

1.2.1 Binary Arithmetic 24

1.2.2 Hexadecimal Arithmetic 27

1.3 Base Conversions 29

1.3.1 Conversion Methods and Algorithms 29

1.3.2 Conversion between Base A and Base B When B = Ak 32

1.4 Signed Number Representation 33

1.4.1 Sign Magnitude Numbers 33

1.4.2 Complementary Number Systems 35

1.5 Digital Codes 45

1.5.1 Numeric Codes 46

1.5.2 Character and Other Codes 50

1.5.3 Error Detection and Correction Codes 53

1.6 Summary and Review Questions 58

1.7 Collaboration Activities 58

Problems 59

2 Logic Circuits and Boolean Algebra 61

Learning Objectives 61

2.1 Logic Gates and Logic Circuits 61

2.1.1 Truth Tables 61

2.1.2 Basic Logic Gates 62

2.1.3 Combinational Logic Circuits 65

2.1.4 Sequential Logic Circuits 68

2.2 Hardware Description Languages (HDLs) 69

2.2.1 Verilog 69

2.2.2 VHDL 70

2.3 Boolean Algebra 72

2.3.1 Postulates and Fundamental Theorems 72

2.3.2 Boolean (Logic) Functions and Equations 77

2.3.3 Minterms, Maxterms, and Canonical Forms 78

2.3.4 Incompletely Specified Functions (Don’t Cares) 81

2.4 Minimization of Logic Expressions 82

2.4.1 Minimization Goals and Methods 82

2.4.2 Karnaugh Maps (K-Maps) 84

2.4.3 Minimization of Logic Expressions Using K-Maps 91

2.4.4 Quine–McCluskey Method 106

2.5 Summary and Review Questions 111

2.6 Collaboration Activities 112

Problems 113

3 Combinational Logic Circuit Design and Analysis 123

Learning Objectives 123

3.1 Design of Combinational Logic Circuits 123

3.1.1 AND–OR and NAND–NAND Circuits 124

3.1.2 OR–AND and NOR–NOR Circuits 125

3.1.3 Two-Level Circuits 126

3.1.4 Multilevel Circuits and Factoring 128

3.1.5 EXCLUSIVE-OR (XOR) Circuits 131

3.2 Analysis of Combinational Circuits 134

3.2.1 Boolean Algebra 134

3.2.2 Truth Tables 136

3.2.3 Timing Diagrams 137

3.2.4 Positive and Negative Logic 142

3.3 Design Using Higher-Level Devices 143

3.3.1 Decoders 143

3.3.2 Encoders 155

3.3.3 Multiplexers and Demultiplexers 159

3.3.4 Arithmetic Circuits 169

3.4 Summative Design Examples 182

3.4.1 Design Flow 182

3.4.2 Bank Security-Lock Controller 182

3.4.3 Seven-Segment Display Decoder 186

3.4.4 Four-Function Arithmetic Logic Unit (add, subtract, AND, XOR) 192

3.4.5 Binary Array Multiplier 196

3.5 Summary and Review Questions 200

3.6 Collaboration Activities 201

Problems 202

4 Introduction to Sequential Circuits 213

Learning Objectives 213

4.1 Models and Classes of Sequential Circuits 214

4.1.1 Finite-State Machines 214

4.1.2 State Diagrams and State Tables 216

4.1.3 Algorithmic State Machines 219

4.2 Memory Devices 221

4.2.1 Latches 222

4.2.2 Flip-Flops 234

4.2.3 Latch and Flip-Flop Summary 244

4.3 Registers 244

4.4 Shift Registers 248

4.5 Counters 253

4.5.1 Synchronous Binary Counters 254

4.5.2 Asynchronous Binary Counters 257

4.5.3 Modulo-N Counters 258

4.5.4 Ring and Twisted-Ring Counters 263

4.6 Summative Design Examples 272

4.6.1 Register File 272

4.6.2 Multiphase Clock 273

4.6.3 Digital Timer 275

4.6.4 Programmable Baud Rate Generator 278

4.7 Summary and Review Questions 281

References 281

4.8 Collaboration Activities 282

Problems 283

5 Synchronous Sequential Logic Circuit Analysis and Design 291

Learning Objectives 291

5.1 Analysis of Sequential Circuits 291

5.1.1 Circuit Analysis Using State Diagrams and State Tables 291

5.1.2 Analysis of Sequential Circuit Logic Diagrams 293

5.1.3 Summary 305

5.2 Design of Synchronous Sequential Circuits 305

5.2.1 Design Procedure 306

5.2.2 Flip-Flop Input Tables 309

5.2.3 Design Examples 311

5.2.4 One-Hot Finite-State Machine Design Method 331

5.2.5 Incompletely Specified Sequential Circuits 336

5.3 State Reduction in Sequential Circuits 338

5.3.1 Redundant States 338

5.3.2 State Reduction in Completely Specified Circuits 340

5.4 Summative Design Examples 344

5.4.1 Drink Vending Machine Control Unit 344

5.4.2 Binary Multiplier 347

5.4.3 Traffic Light Controller 350

5.5 Summary and Review Questions 361

References 362

5.6 Collaboration Activities 362

Problems 366

6 Asynchronous Sequential Circuit Analysis and Design 377

Learning Objectives 377

6.1 Types of Asynchronous Circuits 377

6.2 Analysis and Design of Pulse-Mode Circuits 378

6.2.1 Analysis of Pulse-Mode Circuits 379

6.2.2 Design of Pulse-Mode Circuits 384

6.3 Analysis of Fundamental-Mode Circuits 390

6.3.1 Introduction 392

6.3.2 Excitation and Flow Tables 393

6.3.3 Analysis Procedure 394

6.4 Design of Fundamental-Mode Circuits 396

6.4.1 Flow Table Design and Realization 396

6.4.2 Races and Cycles 405

6.4.3 Eliminating Race Conditions 409

6.4.4 Hazards 418

6.5 Summative Design Examples 419

6.5.1 Design Flow 419

6.5.2 Asynchronous Vending Machine Controller 420

6.5.3 Asynchronous Bus Arbiters 422

6.6 Summary and Review Questions 429

6.7 Collaboration Activities 429

Problems 430

7 Programmable Digital Logic Devices 440

Learning Objectives 440

7.1 Programmable Digital Logic Device Technology 440

7.2 Field-Programmable Gate Arrays (FPGAs) 442

7.2.1 Configurable Logic Blocks 443

7.2.2 Input/Output Blocks 452

7.2.3 Interconnect Resources 454

7.2.4 Clock Resources 456

7.2.5 Other FPGA Resources and Options 457

7.2.6 FPGA Design Process and Examples 457

7.3 Programmable Logic Devices (PLDs) 466

7.3.1 Array Structures for Combinational Logic Functions 467

7.3.2 PLD Output and Feedback Options 484

7.3.3 PLDs for Sequential Circuit Applications 489

7.3.4 Complex PLDs (CPLDs) 492

7.3.5 Design Examples 493

7.4 Summative Design Examples 496

7.4.1 Binary Division Circuit 496

7.4.2 Multiplexed Seven-Segment Display Controller 502

7.5 Summary and Review Questions 510

References 510

7.6 Collaboration Activities 511

Problems 513

8 Design of Digital Systems 519

Learning Objectives 519

8.1 Design Processes 519

8.1.1 Hierarchical Design 519

8.1.2 Fixed Logic versus Programmable Logic 521

8.1.3 Digital System Design Flow 521

8.2 Design Examples 521

8.2.1 Tiny RISC 4 (TRISC4) Processor 522

8.2.2 One-Lane Traffic Controller 533

8.2.3 Universal Asynchronous Receiver/Transmitter (UART) 540

8.2.4 Elevator Controller 547

8.3 Summary and Review Questions 552

8.4 Collaboration Activities 552

Problems 552

Appendix A Verilog Primer 554

A.1 Introduction 554

A.2 General Concepts and Modules 554

A.2.1 Module Structure 555

A.2.2 Port Declarations 556

A.2.3 Data Types 556

A.2.4 Numbers 557

A.3 Gate-Level Structural Modeling 557

A.3.1 Gate Types 557

A.3.2 Gate Delays 557

A.4 Dataflow Modeling 558

A.4.1 Expressions, Operands, and Operators 558

A.4.2 Continuous Assignment Statements 558

A.4.3 Continuous Assignment Statement Delay 558

A.5 Behavioral Modeling 560

A.5.1 Procedural Blocks 560

A.5.2 Procedural Assignments 561

A.5.3 Timing Control 562

A.5.4 case Statements 563

A.5.5 if ... else Statements 563

A.5.6 Loop Statements 565

A.5.7 Block Execution 566

A.6 Hierarchical Modeling 567

A.6.1 Functions and Tasks 567

A.6.2 Structural Models 568

A.7 System Tasks and Compiler Directives 569

A.8 Test Benches 570

A.9 Summary of Features 571

References 572

Appendix B VHDL Primer 573

B.1 Introduction 573

B.2 Design Unit Structure 574

B.2.1 Signals and Data Types 574

B.2.2 Operators and Expressions 579

B.2.3 Design Entities 580

B.2.4 Design Architectures 583

B.3 Behavioral and Dataflow Models 583

B.3.1 Concurrent Signal Assignments 583

B.3.2 Signal Delays 584

B.3.3 Conditional Signal Assignments 585

B.3.4 Selected Signal Assignments 586

B.4 Structural and Hierarchical Models 587

B.4.1 Component Declaration 587

B.4.2 Component Instantiation 588

B.5 Mixed Modeling Styles 590

B.6 Modeling Sequential Behavioral 591

B.6.1 Process Construct 591

B.6.2 Sequential Statements 592

B.6.3 Sequential Circuit Models 594

B.6.4 Synchronous and Asynchronous Control Signals 596

B.6.5 Finite-State Machine Models 597

B.6.6 Register Transfer Level (RTL) Design 598

B.7 Subprograms, Packages, and Libraries 600

B.7.1 Functions and Procedures 600

B.7.2 Packages and Libraries 602

B.8 Test Benches 604

B.9 Summary of Features and Keywords 607

References 609

定价:129.0

ISBN:9787121398704

作者:维克多·P·纳尔逊

版次:第1版

出版时间:2020-11

内容提要:

本书以介绍数字设计的基础知识以及丰富案例为主要特色,并在**版的基础上进行了全面的修订与更新,更加突出了数字设计相关技术的应用。本书内容包括:计算机与数字系统,数制系统,逻辑电路与布尔代数,组合逻辑电路分析与设计,时序逻辑电路简介,同步时序逻辑电路分析与设计,异步时序逻辑电路分析与设计,可编程逻辑器件,数字系统设计。本书对基本概念和理论的讲解具有一定的广度与深度,同时添加了非常实用的设计方法。

作者简介:

Victor P. Nelson,美国俄亥俄州立大学电气工程博士,现为奥本大学电气与计算机工程教授。IEEE计算机协会和IEEE教育协会的终身高级会员。Nelson教授出版过多部数字设计方面的教材,发表过大量的文章,并且是多家公司的微处理器应用和容错系统顾问。

Victor P. Nelson,美国俄亥俄州立大学电气工程博士,现为奥本大学电气与计算机工程教授。IEEE计算机协会和IEEE教育协会的终身高级会员。Nelson教授出版过多部数字设计方面的教材,发表过大量的文章,并且是多家公司的微处理器应用和容错系统顾问。

目录:

0 Computers and Digital Systems 1

Learning Objectives 1

0.1 A Brief History of Computing 1

0.1.1 Beginnings: Mechanical Computers 2

0.1.2 Early Electronic Computers 2

0.1.3 The First Four Generations of Computers 2

0.1.4 The Fifth Generation and Beyond 4

0.2 Digital Systems 4

0.2.1 Digital versus Analog Systems 5

0.2.2 Digital System Levels of Abstraction 5

0.3 Electronic Technologies 8

0.3.1 Moore’s “Law” 9

0.3.2 Fixed versus Programmable Logic 10

0.3.3 Microcontrollers 10

0.3.4 Design Evolution 10

0.4 Applications of Digital Systems 12

0.4.1 General-Purpose Digital Computers 12

0.4.2 Controllers 17

0.4.3 Internet of Things (IoT) 18

0.4.4 Interfacing 18

0.5 Summary and Review Questions 20

0.6 Collaboration Activities 20

References 21

1 Number Systems and Digital Codes 22

Learning Objectives 22

1.1 Number Systems 22

1.1.1 Positional and Polynomial Notations 23

1.1.2 Commonly Used Number Systems 23

1.2 Arithmetic 24

1.2.1 Binary Arithmetic 24

1.2.2 Hexadecimal Arithmetic 27

1.3 Base Conversions 29

1.3.1 Conversion Methods and Algorithms 29

1.3.2 Conversion between Base A and Base B When B = Ak 32

1.4 Signed Number Representation 33

1.4.1 Sign Magnitude Numbers 33

1.4.2 Complementary Number Systems 35

1.5 Digital Codes 45

1.5.1 Numeric Codes 46

1.5.2 Character and Other Codes 50

1.5.3 Error Detection and Correction Codes 53

1.6 Summary and Review Questions 58

1.7 Collaboration Activities 58

Problems 59

2 Logic Circuits and Boolean Algebra 61

Learning Objectives 61

2.1 Logic Gates and Logic Circuits 61

2.1.1 Truth Tables 61

2.1.2 Basic Logic Gates 62

2.1.3 Combinational Logic Circuits 65

2.1.4 Sequential Logic Circuits 68

2.2 Hardware Description Languages (HDLs) 69

2.2.1 Verilog 69

2.2.2 VHDL 70

2.3 Boolean Algebra 72

2.3.1 Postulates and Fundamental Theorems 72

2.3.2 Boolean (Logic) Functions and Equations 77

2.3.3 Minterms, Maxterms, and Canonical Forms 78

2.3.4 Incompletely Specified Functions (Don’t Cares) 81

2.4 Minimization of Logic Expressions 82

2.4.1 Minimization Goals and Methods 82

2.4.2 Karnaugh Maps (K-Maps) 84

2.4.3 Minimization of Logic Expressions Using K-Maps 91

2.4.4 Quine–McCluskey Method 106

2.5 Summary and Review Questions 111

2.6 Collaboration Activities 112

Problems 113

3 Combinational Logic Circuit Design and Analysis 123

Learning Objectives 123

3.1 Design of Combinational Logic Circuits 123

3.1.1 AND–OR and NAND–NAND Circuits 124

3.1.2 OR–AND and NOR–NOR Circuits 125

3.1.3 Two-Level Circuits 126

3.1.4 Multilevel Circuits and Factoring 128

3.1.5 EXCLUSIVE-OR (XOR) Circuits 131

3.2 Analysis of Combinational Circuits 134

3.2.1 Boolean Algebra 134

3.2.2 Truth Tables 136

3.2.3 Timing Diagrams 137

3.2.4 Positive and Negative Logic 142

3.3 Design Using Higher-Level Devices 143

3.3.1 Decoders 143

3.3.2 Encoders 155

3.3.3 Multiplexers and Demultiplexers 159

3.3.4 Arithmetic Circuits 169

3.4 Summative Design Examples 182

3.4.1 Design Flow 182

3.4.2 Bank Security-Lock Controller 182

3.4.3 Seven-Segment Display Decoder 186

3.4.4 Four-Function Arithmetic Logic Unit (add, subtract, AND, XOR) 192

3.4.5 Binary Array Multiplier 196

3.5 Summary and Review Questions 200

3.6 Collaboration Activities 201

Problems 202

4 Introduction to Sequential Circuits 213

Learning Objectives 213

4.1 Models and Classes of Sequential Circuits 214

4.1.1 Finite-State Machines 214

4.1.2 State Diagrams and State Tables 216

4.1.3 Algorithmic State Machines 219

4.2 Memory Devices 221

4.2.1 Latches 222

4.2.2 Flip-Flops 234

4.2.3 Latch and Flip-Flop Summary 244

4.3 Registers 244

4.4 Shift Registers 248

4.5 Counters 253

4.5.1 Synchronous Binary Counters 254

4.5.2 Asynchronous Binary Counters 257

4.5.3 Modulo-N Counters 258

4.5.4 Ring and Twisted-Ring Counters 263

4.6 Summative Design Examples 272

4.6.1 Register File 272

4.6.2 Multiphase Clock 273

4.6.3 Digital Timer 275

4.6.4 Programmable Baud Rate Generator 278

4.7 Summary and Review Questions 281

References 281

4.8 Collaboration Activities 282

Problems 283

5 Synchronous Sequential Logic Circuit Analysis and Design 291

Learning Objectives 291

5.1 Analysis of Sequential Circuits 291

5.1.1 Circuit Analysis Using State Diagrams and State Tables 291

5.1.2 Analysis of Sequential Circuit Logic Diagrams 293

5.1.3 Summary 305

5.2 Design of Synchronous Sequential Circuits 305

5.2.1 Design Procedure 306

5.2.2 Flip-Flop Input Tables 309

5.2.3 Design Examples 311

5.2.4 One-Hot Finite-State Machine Design Method 331

5.2.5 Incompletely Specified Sequential Circuits 336

5.3 State Reduction in Sequential Circuits 338

5.3.1 Redundant States 338

5.3.2 State Reduction in Completely Specified Circuits 340

5.4 Summative Design Examples 344

5.4.1 Drink Vending Machine Control Unit 344

5.4.2 Binary Multiplier 347

5.4.3 Traffic Light Controller 350

5.5 Summary and Review Questions 361

References 362

5.6 Collaboration Activities 362

Problems 366

6 Asynchronous Sequential Circuit Analysis and Design 377

Learning Objectives 377

6.1 Types of Asynchronous Circuits 377

6.2 Analysis and Design of Pulse-Mode Circuits 378

6.2.1 Analysis of Pulse-Mode Circuits 379

6.2.2 Design of Pulse-Mode Circuits 384

6.3 Analysis of Fundamental-Mode Circuits 390

6.3.1 Introduction 392

6.3.2 Excitation and Flow Tables 393

6.3.3 Analysis Procedure 394

6.4 Design of Fundamental-Mode Circuits 396

6.4.1 Flow Table Design and Realization 396

6.4.2 Races and Cycles 405

6.4.3 Eliminating Race Conditions 409

6.4.4 Hazards 418

6.5 Summative Design Examples 419

6.5.1 Design Flow 419

6.5.2 Asynchronous Vending Machine Controller 420

6.5.3 Asynchronous Bus Arbiters 422

6.6 Summary and Review Questions 429

6.7 Collaboration Activities 429

Problems 430

7 Programmable Digital Logic Devices 440

Learning Objectives 440

7.1 Programmable Digital Logic Device Technology 440

7.2 Field-Programmable Gate Arrays (FPGAs) 442

7.2.1 Configurable Logic Blocks 443

7.2.2 Input/Output Blocks 452

7.2.3 Interconnect Resources 454

7.2.4 Clock Resources 456

7.2.5 Other FPGA Resources and Options 457

7.2.6 FPGA Design Process and Examples 457

7.3 Programmable Logic Devices (PLDs) 466

7.3.1 Array Structures for Combinational Logic Functions 467

7.3.2 PLD Output and Feedback Options 484

7.3.3 PLDs for Sequential Circuit Applications 489

7.3.4 Complex PLDs (CPLDs) 492

7.3.5 Design Examples 493

7.4 Summative Design Examples 496

7.4.1 Binary Division Circuit 496

7.4.2 Multiplexed Seven-Segment Display Controller 502

7.5 Summary and Review Questions 510

References 510

7.6 Collaboration Activities 511

Problems 513

8 Design of Digital Systems 519

Learning Objectives 519

8.1 Design Processes 519

8.1.1 Hierarchical Design 519

8.1.2 Fixed Logic versus Programmable Logic 521

8.1.3 Digital System Design Flow 521

8.2 Design Examples 521

8.2.1 Tiny RISC 4 (TRISC4) Processor 522

8.2.2 One-Lane Traffic Controller 533

8.2.3 Universal Asynchronous Receiver/Transmitter (UART) 540

8.2.4 Elevator Controller 547

8.3 Summary and Review Questions 552

8.4 Collaboration Activities 552

Problems 552

Appendix A Verilog Primer 554

A.1 Introduction 554

A.2 General Concepts and Modules 554

A.2.1 Module Structure 555

A.2.2 Port Declarations 556

A.2.3 Data Types 556

A.2.4 Numbers 557

A.3 Gate-Level Structural Modeling 557

A.3.1 Gate Types 557

A.3.2 Gate Delays 557

A.4 Dataflow Modeling 558

A.4.1 Expressions, Operands, and Operators 558

A.4.2 Continuous Assignment Statements 558

A.4.3 Continuous Assignment Statement Delay 558

A.5 Behavioral Modeling 560

A.5.1 Procedural Blocks 560

A.5.2 Procedural Assignments 561

A.5.3 Timing Control 562

A.5.4 case Statements 563

A.5.5 if ... else Statements 563

A.5.6 Loop Statements 565

A.5.7 Block Execution 566

A.6 Hierarchical Modeling 567

A.6.1 Functions and Tasks 567

A.6.2 Structural Models 568

A.7 System Tasks and Compiler Directives 569

A.8 Test Benches 570

A.9 Summary of Features 571

References 572

Appendix B VHDL Primer 573

B.1 Introduction 573

B.2 Design Unit Structure 574

B.2.1 Signals and Data Types 574

B.2.2 Operators and Expressions 579

B.2.3 Design Entities 580

B.2.4 Design Architectures 583

B.3 Behavioral and Dataflow Models 583

B.3.1 Concurrent Signal Assignments 583

B.3.2 Signal Delays 584

B.3.3 Conditional Signal Assignments 585

B.3.4 Selected Signal Assignments 586

B.4 Structural and Hierarchical Models 587

B.4.1 Component Declaration 587

B.4.2 Component Instantiation 588

B.5 Mixed Modeling Styles 590

B.6 Modeling Sequential Behavioral 591

B.6.1 Process Construct 591

B.6.2 Sequential Statements 592

B.6.3 Sequential Circuit Models 594

B.6.4 Synchronous and Asynchronous Control Signals 596

B.6.5 Finite-State Machine Models 597

B.6.6 Register Transfer Level (RTL) Design 598

B.7 Subprograms, Packages, and Libraries 600

B.7.1 Functions and Procedures 600

B.7.2 Packages and Libraries 602

B.8 Test Benches 604

B.9 Summary of Features and Keywords 607

References 609

- 电子工业出版社有限公司

- 电子工业出版社有限公司有赞官方供货商,为客户提供一流的知识产品及服务。

- 扫描二维码,访问我们的微信店铺